# Insight into the multicomponent nature of negative bias temperature instability

Duc D. Nguyen, Camron Kouhestani, Kenneth E. Kambour, and Roderick A. B. Devine

Citation: Journal of Vacuum Science & Technology B 31, 030601 (2013); doi: 10.1116/1.4796115

View online: http://dx.doi.org/10.1116/1.4796115

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/31/3?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

# Articles you may be interested in

Physical understanding of negative bias temperature instability below room temperature J. Appl. Phys. **112**, 104514 (2012); 10.1063/1.4767623

Negative-bias temperature instability induced electron trapping

Appl. Phys. Lett. 93, 033512 (2008); 10.1063/1.2963368

Physical mechanisms of negative-bias temperature instability

Appl. Phys. Lett. 86, 142103 (2005); 10.1063/1.1897075

Reaction-dispersive proton transport model for negative bias temperature instabilities

Appl. Phys. Lett. 86, 093506 (2005); 10.1063/1.1871357

Nitrogen-enhanced negative bias temperature instability: An insight by experiment and first-principle calculations Appl. Phys. Lett. **82**, 1881 (2003); 10.1063/1.1563045

## LETTERS

# Insight into the multicomponent nature of negative bias temperature instability

Duc D. Nguyen and Camron Kouhestani

COSMIAC, Air Force Research Laboratory, Space Vehicles Directorate, Electronic Foundations Group, Bldg. 914, Kirtland AFB, New Mexico 87117

# Kenneth E. Kambour<sup>a)</sup>

SAIC, Air Force Research Laboratory, Space Vehicles Directorate, Electronic Foundations Group, Bldg. 914, Kirtland AFB, New Mexico 87117

### Roderick A. B. Devine

Think Strategically, Air Force Research Laboratory, Space Vehicles Directorate, Electronic Foundations Group, Bldg. 914, Kirtland AFB, New Mexico 87117

(Received 30 January 2013; accepted 8 March 2013; published 22 March 2013)

A novel measurement technique is used to extract two physically distinct "permanent" (long lived on our experimental time scale,  $\leq 12~000~\text{s}$ ) and one recoverable charge components of the negative bias temperature instability in p-channel metal-oxide-semiconductor field effect transistors under inversion and n-channel devices under accumulation. The results suggest that the permanent components are present in both cases, while there is little, if any, recoverable charge present in the case of the n-channel device. A physical explanation is provided involving the band energy diagram to explain these observations. © 2013 American Vacuum Society. [http://dx.doi.org/10.1116/1.4796115]

#### I. INTRODUCTION

It is widely accepted that the negative bias temperature instability (NBTI) in p-channel MOSFETs (PMOS)<sup>1,2</sup> results in a threshold voltage<sup>3</sup> shift,  $\Delta V_{th}$ , which is comprised of at least two terms. These terms are assumed to be associated with positively charged interface states ( $\Delta V_{th}(IS)$ ) and positively charged defects in the gate oxide structure ( $\Delta V_{th}(RC)$ ). The latter are termed "recoverable charge" (RC) because removal of the negative stressing voltage applied to the MOSFET gate results in spontaneous relaxation and disappearance of the  $\Delta V_{th}(RC)$  component. We have recently reported<sup>4</sup> the results of a study of NBTI using an experimental methodology which allows extraction of the individual components of  $\Delta V_{th}$  and evidenced a third component which is field recoverable charge,  $\Delta V_{th}(FRC)$ . This component is observed to disappear if relaxation takes place in the presence of a small positive potential but to re-appear if a small negative potential is subsequently applied. The negative potential was not significant enough to generate an NBTI response in itself. The FRC behavior was then associated with switching traps<sup>5,6</sup> in which a trapped positive charge was compensated by a trapped negative charge resulting from electron tunneling in the presence of the positive potential. In the usual model for oxide-related switching traps,<sup>5</sup> both RC and FRC are derivatives of a neutral oxygen vacancy center termed<sup>7</sup> the E' center. At the present time, it is assumed that the RC component of NBTI is a result of hole tunneling from the PMOS inversion layer into neutral traps located in the gate oxide/dielectric, although the exact location in space/energy is

#### II. EXPERIMENTAL PROCEDURE

Both the PMOS and NMOS devices used in the experiments reported here had nominal 130 nm channel lengths,  $5 \,\mu \text{m}$  channel widths, and 3.4 nm thick silicon oxynitride gate insulators. Measurements were carried out at several temperatures, but only 90°C data will be shown here. A Keithley Instruments, Inc. 4200-SCS semiconductor characterization system was used to acquire data. Two modes of operation were used.<sup>4</sup> The first corresponded to a "pseudo" continuous stressing mode in which a voltage (Vgs) is applied to the MOSFET gate contact with respect to the source and body contacts. At time t = 0 s, the  $V_{\rm gs}$  is ramped to some prechosen measurement value  $(V_{\text{gs}(m)})$  with a rise time of typically 20 ns. At the same time, the source-drain voltage,  $V_{ds}$ , is ramped from 0 to -0.05 V (0.05 V for the NMOS), and the source-drain current, I<sub>ds</sub>, is then measured in an acquisition time window,  $\tau_{\rm m}\!\sim\!4\,\mu{\rm s}.$  This first measurement establishes  ${I_{ds}}^{\circ} \! = \! I_{ds}(t \! = \! 0 \, s).$  The device is then stressed for some chosen time,  $\tau_{\text{stress}}$ , with a gate voltage

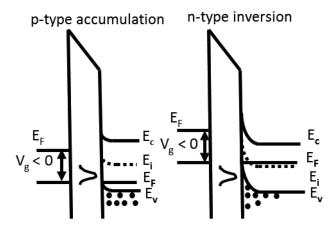

not known. Hole tunneling should also result from accumulation layers in a negatively biased n-channel MOSFETs (NMOS) device although, as shown schematically in Fig. 1, the position in energy of the holes in the silicon valence band should be different, therein enabling a crude form of defect spectroscopy. With this philosophy, we have performed NBTI measurements on n-channel MOSFETs subjected to stress in the accumulation condition then measured in inversion. This work complements a study performed<sup>8</sup> on PMOS and NMOS devices with substantially thicker, pure SiO<sub>2</sub> gate dielectrics. Preliminary results of the study are reported in the following.

a) Electronic mail: Kenneth.Kambour.ctr@Kirtland.af.mil

Fig. 1. Schematic representation of the bands for accumulation in an NMOS (p-type substrate) (left) and inversion in a PMOS (n-type substrate) (right). The recoverable charge defects are crudely represented by the distribution shown in the oxide. Note that tunneling of the holes (•) to the defect states is less likely in the NMOS accumulation case than in the PMOS inversion case.

$V_{gs(stress)}$  ( $V_{ds}\!=\!V_{sb}\!=\!0\,V$ ), after which a measurement sequence is again performed to determine  $I_{ds}(\tau_{stress})$ . The process is then repeated and the cumulative variation of  $I_{ds}(t_{stress})$  (with  $t_{stress}\!=\!\Sigma\,\tau_{stress}$ ) determined and converted to  $\Delta V_{th}(t_{stress})$ . This measurement is analogous to the "on the fly" method where  $I_{ds}$  is measured at  $V_{gs(stress)}$ . However, our approach has the advantage that  $I_{ds}$  is measured with  $|V_{gs(m)}|\!<\!|V_{gs(stress)}|$ , which removes a potential source of measurement error.

The second method of stressing uses a pulse stream. In this case, the  $V_{gs(stress)}$  applied during the  $\tau_{stress}$  is a series of stress  $(\tau_{on})$  and recovery  $(\tau_{off})$  pulses with a duty cycle  $D = \tau_{on}/(\tau_{on} + \tau_{off})$ . With the system available, a measurement was made at  $V_{gs(m)}$  immediately following a  $\tau_{off}$  recovery period. The total stressing time,  $t_{stress}$ , was  $N\tau_{on}$ , where N was the number of pulses. During the final  $\tau_{\rm off}$  part of each pulse, dynamic or recoverable charge detrapping can occur. If this time is long enough, the influence of  $V_{gs(stress)}$  on the I<sub>ds</sub> measured corresponds only to that part associated with "permanent" charge trapping. For these experiments, D = 10% is chosen following a series of short stress time experiments (<0.01 s) in which permanent charge trapping was estimated to be small in order to see if there was a buildup of recoverable charge after repeated cycles. Similar testing demonstrated that the use of  $V_{recovery} \ge 1 \text{ V}$  during the 90% of the pulse time allocated to recovery resulted in full relaxation of the FRC and RC terms. This approach provides a direct method for determination of the permanent interface charge trapping independently of any recoverable part.

#### III. RESULTS AND DISCUSSION

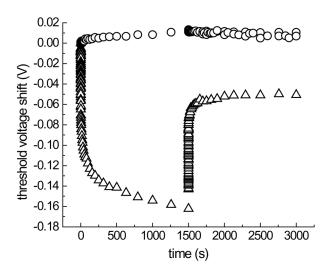

The charging due to the application of  $-3.50\,\mathrm{V}$  stressing for  $1500\,\mathrm{s}$  followed by  $1500\,\mathrm{s}$  of relaxation at  $0.0\,\mathrm{V}$  is shown ( $\Delta$ ) for the PMOS studied at  $90\,^\circ\mathrm{C}$  in Fig. 2. (This represents customary accelerated stress testing for NBTI, necessary to obtain voltage shifts large enough to measure experimentally in a physically acceptable time frame. The relative importance of the individual components will clearly depend on

Fig. 2. Measured threshold voltage shift due to NBTI at 90 °C for a PMOS ( $\Delta$ ) and NMOS (O) stressed for 1500 s at  $V_{gs}=-3.50$  and -3.75 V, respectively, followed by 1500 s of relaxation at  $V_{gs}=0$  V.

their respective field and temperature dependencies. This variability is presently being studied.) Conversion of the measured variation of  $I_{ds}$  into the presented parameter  $\Delta V_{th}$  was performed using different methods, including the linear approximation<sup>7</sup>

$$\Delta V_{th} = (1 - I_{ds}/I_{ds}^{\circ})(V_{gs(m)} - V_{th}^{\circ}), \tag{1}$$

in which  $V_{gs(m)}$  is the measurement voltage,  $V_{th}{}^{\circ}$  is the prestress threshold voltage and  $I_{ds}{}^{\circ}$  is the source-drain current at time  $t=0\,s.$  Typically,  $V_{gs(m)}=-0.52\,V$  and  $V_{th}{}^{\circ}\sim-0.40\,V$  for the PMOS and  $V_{gs(m)}=0.52\,V$  and  $V_{th}{}^{\circ}\sim0.38\,V$  for the NMOS.

The appropriate bias to correspond to the same oxide field is a subject of some disagreement. However, based on the work of Schroeder<sup>10</sup> and simulations performed using the Silvaco Atlas device simulation code, an NBTI bias for the NMOS of  $-3.75\,\mathrm{V}$  was chosen (corresponding to  $-3.50\,\mathrm{V}$  for the PMOS). The results for  $\Delta\mathrm{V}_{th}$  as a function of time for 1500 s of bias stress followed by 1500 s of relaxation at 0 V are shown in Fig. 2. The (O) symbols apply to the case of the NMOS and the ( $\Delta$ ) to the PMOS.

The most striking difference between the PMOS and NMOS results is the absence of any appreciable RC term for the NMOS. This suggests that, as indicated in Fig. 1, the RC-associated traps must be energetically unfavorable for hole tunneling from the accumulation layer in the case of the NMOS but favorable for tunneling from the inversion layer in the PMOS. To reiterate, it can be seen in the schematic band diagram that for both cases, the surface potential, or band bending, in the inversion channel is much larger than the corresponding potential in the NMOS in accumulation. This means that typically only traps within  $\sim 0.2 \, \text{eV}$  of the Si valence band energy can be reached in the accumulation device, while the device in inversion can access traps substantially higher than the valence band energy. The absence of RC component associated with the NMOS in accumulation leads one to question if the FRC component is also absent.

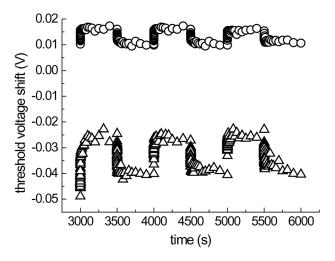

Fig. 3. Measured threshold voltage shift at 90 °C for a PMOS ( $\Delta$ ) and NMOS (O) for oscillating positive (+1.5 V) and negative (-1.0 V) gate biasing following the 1500 s of stress and 1500 s of relaxation shown in Fig. 2.

We recall that initial identification<sup>5,6,11</sup> of the origin of FRC switching traps and RC traps was as derivatives of the E' oxygen vacancy center. One might therefore expect the FRC component to be also absent in the NMOS case. To address this, a  $500 \, \text{s}$  stress at  $+1.5 \, \text{V}$  followed by further stress at  $-1.0\,\mathrm{V}$  was applied immediately following the stress and relaxation sequence shown in Fig. 2. The results are shown in Fig. 3 for both PMOS and NMOS. Whilst there is a difference in the magnitude of the FRC component between the two (20 and 8 mV respectively), the behavior is qualitatively similar, caused by permanent trapped positive charge in the oxide. However, we know that that there is a net positive threshold voltage shift in the NMOS due to negatively charged interface states (see Fig. 4) dominating the FRC component. Based on these observations, we conclude that there is no justification for the hypothesis that the traps resulting in FRC are in any way correlated with those responsible for RC traps.

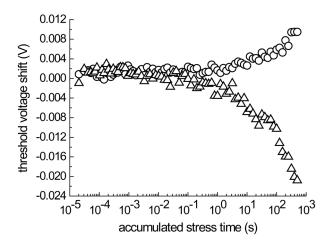

We have hypothesized that one can independently measure the interface state related  $\Delta V_{th}(IS)$  component of  $\Delta V_{th}$  using an alternating stress with a duty cycle of 0.1. These

Fig. 4. Measured IS component of the threshold voltage shift at 90 °C for a PMOS ( $\Delta$ ) and NMOS (O) as a function of accumulated stress time.

measurements were performed for both the PMOS and NMOS with stressing at -3.50 and -3.75 V, respectively, and recovery at 1.5 V for a total stressing time of 1000 s. (The total measurement time was 10 000 s.) The results are shown in Fig. 4. The positive threshold voltage shift for the NMOS case and negative shift for the PMOS are consistent with radiation data on NMOS and PMOS devices, 12 where it has been argued that holes in both cases generate neutral interface states. The position of the Fermi level during measurement of the device source-drain current during operation, above Si midgap for the NMOS and below midgap for the PMOS, leads to negative charging of the interface in the former ( $\Delta V_{th}(IS)$  positive) and positive ( $\Delta V_{th}(IS)$  negative) in the latter. It remains to explain the nature and generation mechanism of the interface states which become charged during the measurement phase. Various authors have proposed models for interface state generation, including strained interfacial bond rupture 13 and proton assisted depassivation of dangling bonds at the interface. From our experiments, we are unable to resolve this dilemma. However, we note that the neutral dangling bond, Si\*, is an amphoteric trap usually termed a Pb center which can therefore appear negative in an NMOS and positive in a PMOS. Following other authors, the threshold voltage shifts in Fig. 4 were fitted to a power law<sup>1,2</sup>

$$\Delta V_{th} = A\,t^\alpha, \tag{2}$$

where  $A=-0.0020\pm0.0002\,V$  and  $\alpha=0.38\pm0.02$  for the PMOS and  $A=0.0025\pm0.0001\,V$  and  $\alpha=0.19\pm0.01$  for the NMOS.

#### IV. SUMMARY

We have performed NBTI measurements on both NMOS and PMOS devices. Our results clearly indicate that the PMOS biased in inversion has at least three positively charged defects: recoverable charge associated with oxide traps, interface states, and field recoverable charge. In NMOS devices, we observe positively charged field recoverable charge and negatively charged interface states. Recoverable charge is absent in the NMOS case. This result suggests that FRC and RC traps do not have a common origin but that interface states and FRC may in fact be linked.

## **ACKNOWLEDGMENTS**

The authors gratefully acknowledge correspondence with Tibor Grasser, Ph.D., of the Technical University of Vienna, Austria, and conversations with L. Trombetta, Ph.D., of the University of Houston and H. Hjalmarson, Ph.D., of Sandia National Laboratories. The work performed by D.D.N. and C.K. is based on research sponsored by the Air Force Research Laboratory under agreement number FA9453-08-2-0259. The work performed by K.E.K. was supported by the U.S. Air Force under a contract sponsored, monitored, and managed by United States Air Force Air Force Material Command, Air Force Research Laboratory, RVSE, Kirtland AFB, NM 87117-5776.

- <sup>1</sup>S. Mahapatra, P. B. Kumar, and M. A. Alam, IEEE Trans. Electron Devices **51**, 1371 (2004).

- <sup>2</sup>A. E. Islam, H. Kufluoglu, D. Varghese, S. Mahapatra, and M. A. Alam, IEEE Trans. Electron Devices **54**, 2143 (2007).

- <sup>3</sup>S. M. Sze, *The Physics of Semiconductor Devices* (Wiley & Sons, NY, 1981) Chap. 8.

- <sup>4</sup>D. D. Nguyen, C. Kouhestani, K. E. Kambour, H. P. Hjalmarson, and R. A. B. Devine, Phys. Status Solidi C 10, 259 (2013).

- <sup>5</sup>A. J. Lelis and T. R. Oldham, IEEE Trans. Nucl. Sci. **41**, 1835 (1994).

- <sup>6</sup>Z. Q. Teo, A. A. Boo, D. S. Ang, and K. C. Leong, IRPS 11, 943 (2011).

- <sup>7</sup>C. J. Nicklaw, Z.-Y. Lu, D. M. Fleetwood, R. D. Schrimpf, and S. T. Pantelides, IEEE Trans. Nucl. Sci. **49**, 2667 (2002).

- <sup>8</sup>T. Aichinger, M. Nelhiebel, and T. Grasser, IEEE Trans. Electron Devices **56**, 3018 (2009).

- <sup>9</sup>D. D. Nguyen, "Understanding one of the dominant failure mechanisms in nanoscale transistors for space-electronics: Negative bias temperature instability," Master's thesis (University of New Mexico, 2013) (unpublished).

- <sup>10</sup>D. K. Schroder, Microelectron. Reliab. 47, 841 (2007).

- <sup>11</sup>D. M. Fleetwood, H. D. Xiong, Z.-Y. Lu, C. J. Nicklaw, J. A. Felix, R. D. Schrimpf, and S. T. Pantelides, IEEE Trans. Nucl. Sci. 49, 2674 (2002).

- <sup>12</sup>T. Stanley, D. Neamen, P. Dressendorfer, J. Schwank, P. Winokur, M. Ackermann, K. Jungling, C. Hawkins, and W. Grannemann, IEEE Trans. Nucl. Sci. NS-32, 3982 (1985).

- <sup>13</sup>S. K. Lai, J. Appl. Phys. **54**, 2540 (1983).